Analysesoftware Xpedition AMSSimulationProjektentwicklungTest

Zu meinen Favoriten hinzufügen

Zum Produktvergleich hinzufügen

Eigenschaften

- Funktion

- Analyse, Simulation, Projektentwicklung, Test, Steuerung, Planung, Ausgabe, Buchführung, Solver, für Schema-Design

- Anwendung

- Prozess, Baustellen, PCB

- Typ

- 3D, automatisiert

- Weitere Eigenschaften

- elektromagnetisch

Beschreibung

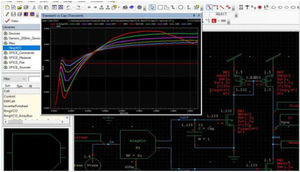

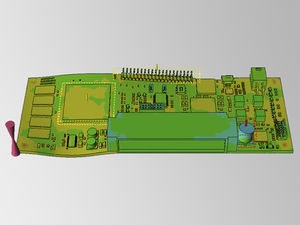

Jede Leiterplatte hat Widerstands-, Kapazitäts- und Induktivitätswerte, die mit Leiterbahnen verbunden sind. Parasitäre Elemente auf Leiterplattenebene können die Leistung der Schaltung negativ beeinflussen - auch wenn ihre Werte gering sind, kann ihre kumulative Wirkung auf die Designleistung erheblich sein. Wenn die Parasiten auf der Leiterplatte während der Entwurfssimulationen nicht modelliert werden, ist ihre Auswirkung auf den Schaltungsbetrieb erst beim Testen des physischen Prototyps bekannt, wo es teuer ist, Änderungen vorzunehmen.

Xpedition Analog / Mixed Signal (AMS) Analyse

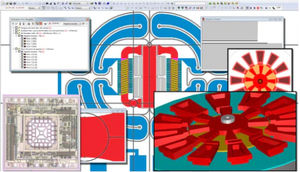

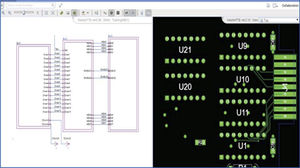

Siemens hat Xpedition AMS mit HyperLynx Advanced 3D Electromagnetic Solvers integriert, um eine einzigartige und leistungsstarke Lösung für die Berechnung von Layout-Parasiten und die Analyse ihrer Auswirkungen auf die Funktion einer Schaltung zu bieten - bevor wertvolle Ressourcen für die Herstellung und den Test von Prototypen eingesetzt werden. Durch die Integration wird die Analyse der Störeinflüsse auf Leiterplattenebene in den Schaltungsentwurfsprozess integriert, wo es am effizientesten ist, Designänderungen vorzunehmen. Die Berücksichtigung von Layout-Störungen zu einem frühen Zeitpunkt im Designprozess verringert das Risiko nachgelagerter Design-Iterationen und ist der Schlüssel dazu, ein Projekt im Zeit- und Kostenrahmen zu halten und die Spezifikationen einzuhalten.

Vorteile der Extraktion von PCB-Parasiten

Genaue Modellierung der Auswirkungen von Leiterbahnen auf die Leistung von Hochgeschwindigkeitsfiltern, Verstärkern, A/D-, D/A- und anderen rauschempfindlichen Designs

Analysieren Sie die Auswirkungen von PCB-Störungen im Zeit- und Frequenzbereich

Bewertung alternativer Leiterplattenlayouts zur Maximierung der Schaltungsleistung

Vollständige Integration von Systemdesignerfassung und Mixed-Signal-Simulation mit PCB-Layout

Der vollautomatische 3D-Extraktionsprozess erfordert keine tiefgreifenden Kenntnisse im Bereich Field Solver

---

Kataloge

Für dieses Produkt ist kein Katalog verfügbar.

Alle Kataloge von Siemens EDA anzeigenVerwandte Suchbegriffe

- Automatisierungs-Softwarelösung

- Management-Softwarelösung

- Analysesoftwarelösung

- Windows-Softwarelösung

- Software für Architektur

- Prozess-Softwarelösung

- Steuerungssoftwarelösung

- Online-Software

- Echtzeit-Softwarelösung

- 3D-Softwarelösung

- Projektentwicklungs-Softwarelösung

- Messsoftware

- Überwachungssoftwarelösung

- Schnittstellen-Software

- Software für Industrieanwendungen

- Qualitätssoftware

- Simulationssoftware

- Visualisierungs-Softwarelösung

- Automatisierte Softwarelösung

- Entwicklungssoftwarelösung

* Die Preise verstehen sich ohne MwSt., Versandkosten und Zollgebühren. Eventuelle Zusatzkosten für Installation oder Inbetriebnahme sind nicht enthalten. Es handelt sich um unverbindliche Preisangaben, die je nach Land, Kurs der Rohstoffe und Wechselkurs schwanken können.